| 前页 | 后页 |

状态机建模For HDLs

要从状态机模型高效地生成硬件描述语言 (HDL) 代码,请应用本主题中描述的设计实践。硬件描述语言包括 VHDL、Verilog 和 SystemC。

在 HDL状态机模型中,您可能期望:

- 指定驾驶触发器

- 建立端口-触发器映射

- 添加到活动状态逻辑

操作

手术 |

描述 |

也见 |

|---|---|---|

|

指定驾驶触发器 |

|

状态机 触发器 |

|

建立端口触发映射 |

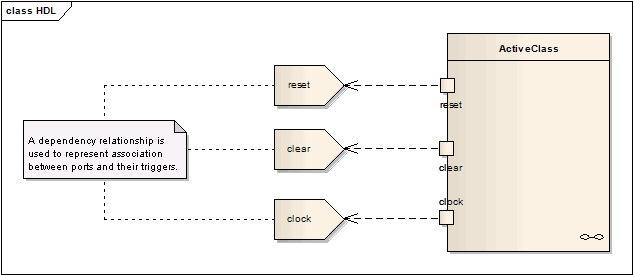

在成功地对组件的不同操作模式进行建模,并将触发器与它们关联起来后,您必须将触发器与组件的端口相关联。 从端口到关联A触发器关系用于表示该关联。 |

|

|

主动状态逻辑 |

指定驱动触发器并建立 Port-Trigger 映射为有效解释硬件组件所需的准备工作做好了准备。 我们现在模型Active (现在)状态中的实际状态机逻辑。 |

注记

- 为了能够从行为模型生成代码,所有行为构造都应该包含在一个类中

- 当前的代码生成引擎只支持一个组件的时钟触发器